1 Introduction

Representing Fudan University, my teammates and I took part in the National Student Computer System Capability Challenge (NSCSCC) a.k.a. “Loongson Cup”. It is a national contest where teams from top universities like Tsinghua University, University of Science and Technology of China compete to build a best CPU. After over a month of work, our “Vanilla” CPU won Second Prize for great performance and compatibility. It was the first time for a team from Fudan to take part in the contest.

2 Background

Details of the task

We were to run our CPU on a piece of Xilinx FPGA. The peripherals were provided and we can focus on the CPU core. Memory access latencies were simulated by a 20x penalty so memory accesses needed to be optimized. Running on FPGA, the CPU needs to pass a series of tests to prove that it correctly implements a specified subset of the MIPS32 instruction set. Then, the CPU is tested on benchmarks to demonstrate its performance. Moreover, programs like bootloaders and simple operating systems are run on the CPU to check its compatibility.

My role

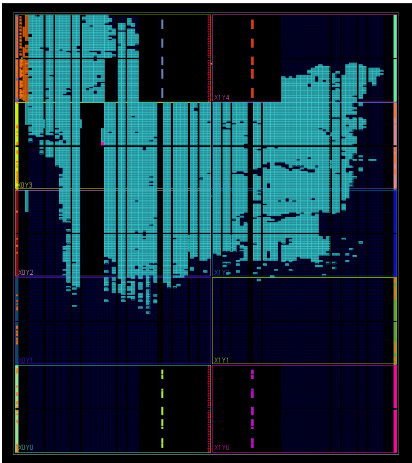

Typically, a CPU in this contest consists of a main pipeline and a cache. I designed and implemented a substantial portion of the main pipeline, writing in SystemVerilog. Also, I merged all parts of the system (the pipeline, cache, AXI interface, etc.) every now and then in the development cycles. After merging into the complete system, I ran tests, identified bugs and looked for possible improvements from a global perspective.

3 Results

- Supports the MIPS revision 1 instruction set: around 80 instructions and various exception handling mechanisms.

- Instruction cache and data cache: over 30x speedup.

- Translation Lookaside Buffer (TLB) with 32 entries.

- Frequency on FPGA: 95 MHz, a result of balancing between IPC (Instructions Per Cycle).

- Capable of running the PMON bootloader.

- Implemented an experimental dual-issue version of the pipeline (didn’t use it in the final version due to various reasons).